March 2007 Rev 2.0.0

#### GENERAL DESCRIPTION

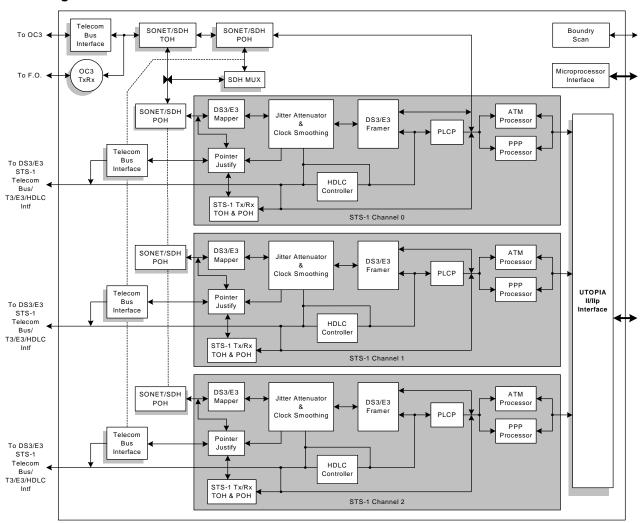

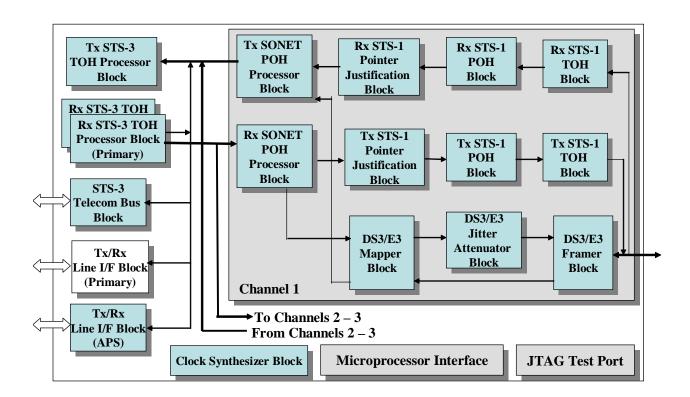

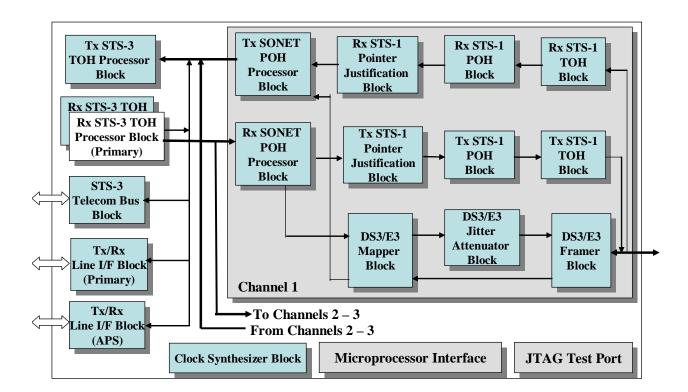

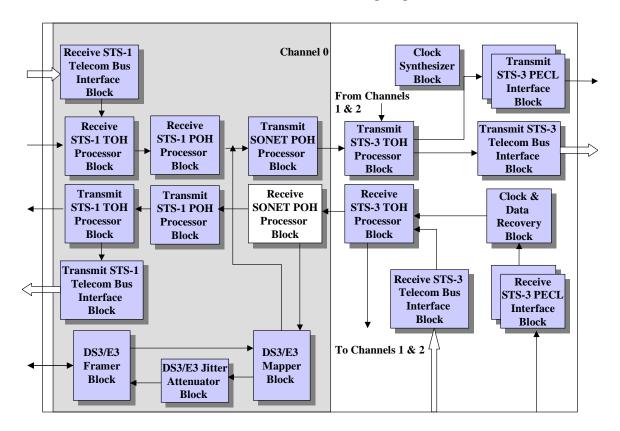

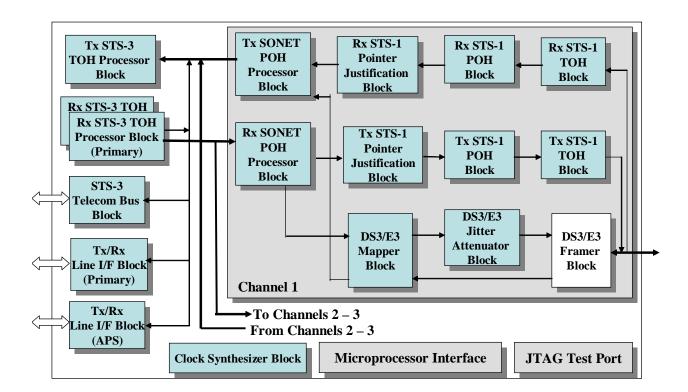

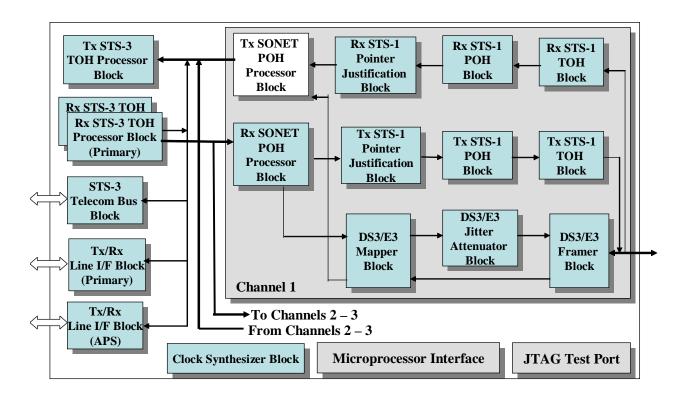

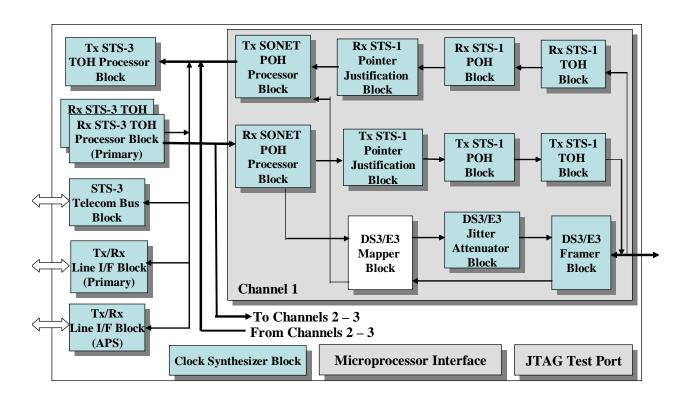

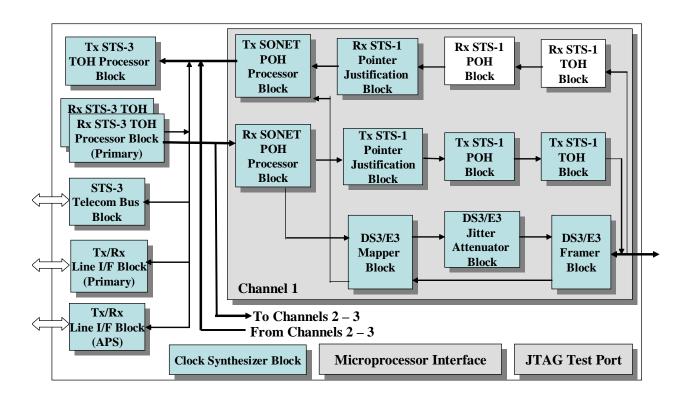

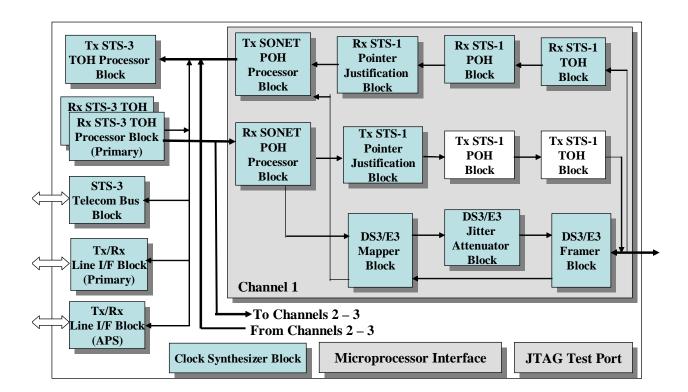

The XRT94L33 is a highly integrated SONET/SDH terminator designed for E3/DS3/STS-1 mapping/de-mapping functions from either the STS-3 or STM-1 data stream. The XRT94L33 interfaces directly to the optical transceiver

The XRT94L33 processes the section, line and path overhead in the SONET/SDH data stream and also performs ATM and PPP PHY-layer processing. The processing of path overhead bytes within the STS-1s or TUG-3s includes 64 bytes for storing the J1 bytes. Path overhead bytes can be accessed through the microprocessor interface or via serial interface.

The XRT94L33 uses the internal E3/DS3 De-Synchronizer circuit with an internal pointer leak algorithm for clock smoothing as well as to remove the jitter due to mapping and pointer movements. These De-Synchronizer circuits do not need any external clock reference for its operation.

The SONET/SDH transmit blocks allow flexible insertion of TOH and POH bytes through both Hardware and Software. Individual POH bytes for the transmitted SONET/SDH signal are mapped either from the XRT94L33 memory map or from external interface. A1, A2 framing pattern, C1 byte and H1, H2 pointer byte are generated.

The SONET/SDH receive blocks receive SONET STS-3 signal or SDH STM-1 signal and perform the necessary transport and path overhead processing.

The XRT94L33 provides a line side APS (Automatic Protection Switching) interface by offering redundant receive serial interface to be switched at the frame boundary.

The XRT94L33 provides 3 Mappers for performing STS-1/VC-3 to STS-1/DS3/E3 mapping function, one for each STS-1/DS3/E3 framers.

A PRBS test pattern generation and detection is implemented to measure the bit-error performance.

A general-purpose microprocessor interface is included for control, configuration and monitoring.

#### **APPLICATIONS**

- Network switches

- Add/Drop Multiplexer

- W-DCS Digital Cross Connect Systems

#### **FEATURES**

- Provides DS3/ E3 mapping/de-mapping for up to 3 tributaries through SONET STS-1 or SDH AU-3 and/or TUG-3/AU-4 containers

- Generates and terminates SONET/SDH section, line and path layers

- Integrated SERDES with Clock Recovery Circuit

- Provides SONET frame scrambling and descrambling

- Integrated Clock Synthesizer that generates 155 MHz and 77.76 MHz clock from an external 12.96/19.44/77.76 MHz reference clock

- Integrated 3 E3/DS3/STS-1 De-Synchronizer circuit that de-jitter gapped clock to meet 0.05Ulpp jitter requirements

- Access to Line or Section DCC

- Level 2 Performance Monitoring for E3 and DS3

- Supports mixing of STS-1E and DS3 or E3 and DS3 tributaries

- UTOPIA Level 2 interface for ATM or level 2P for Packets

- E3 and DS3 framers for both Transmit and Receive directions

- Complete Transport/Section Overhead Processing and generation per Telcordia and ITU standards

- Single PHY and Multi-PHY operations supported

- Full line APS support for redundancy applications

- Loopback support for both SONET/SDH as well as E3/DS3/STS-1

- Boundary scan capability with JTAG IEEE 1149

- 8-bit microprocessor interface

- 3.3 V ± 5% Power Supply; 5 V input signal tolerance

- -40°C to +85°C Operating Temperature Range

- Available in a 504 Ball TBGA package

# EXAR Experience Our Connectivity

#### 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER - SONET REGISTERS

Rev 2.0.0

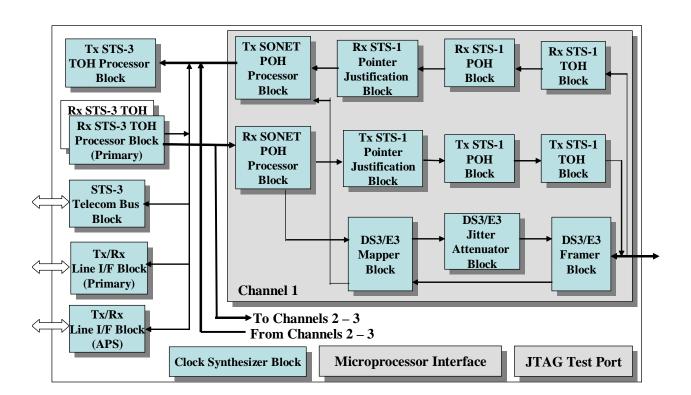

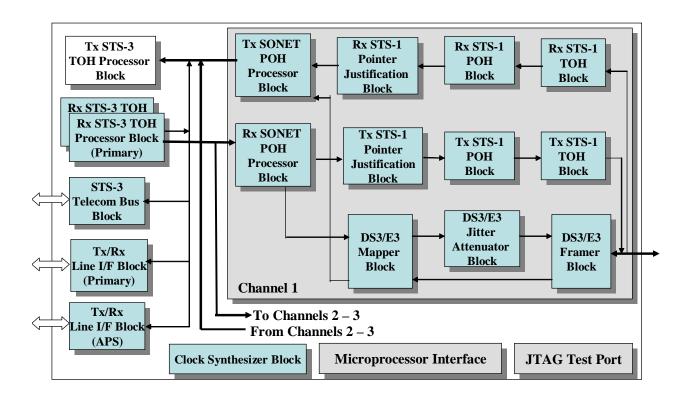

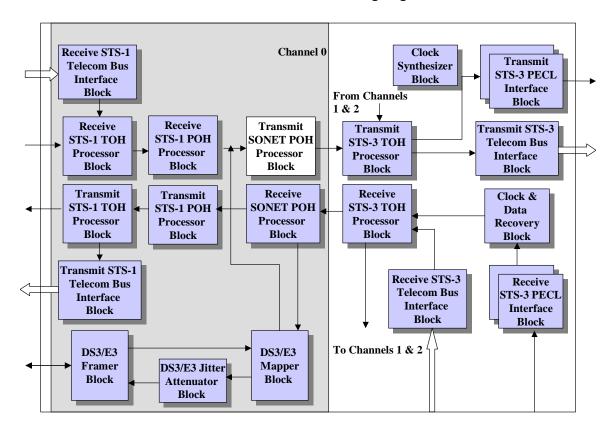

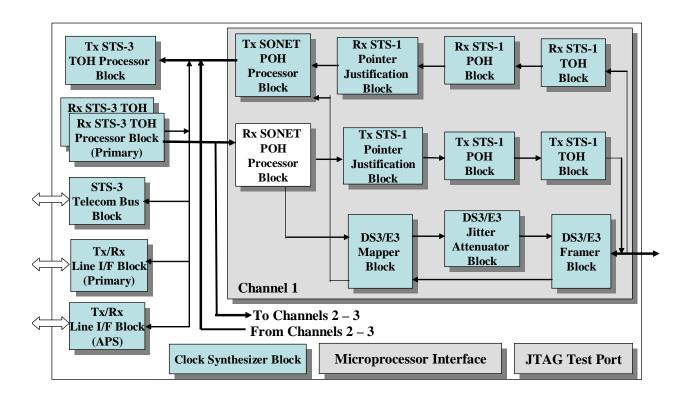

#### **Block Diagram of the XRT94L33**

#### **ORDERING INFORMATION**

| PART NUMBER | PACKAGE TYPE          | OPERATING TEMPERATURE RANGE |

|-------------|-----------------------|-----------------------------|

| XRT94L33IB  | 27 x 27 504 Lead TBGA | -40°C to +85°C              |

#### 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER - SONET REGISTERS

### 1.0 XRT94L33 REGISTERS FOR SONET

#### 1.1 THE OVERALL REGISTER MAP WITHIN THE XRT94L33

The XRT94L33 employs a direct Addressing Scheme. The Address Locations for each of the "Register Groups" (or Register pages) is presented in the Table below.

Table 1: The Address Register Map for the XRT94L33

| Address Location | REGISTER NAME                                                            | DEFAULT VALUE |

|------------------|--------------------------------------------------------------------------|---------------|

|                  | OPERATION CONTROL BLOCK REGISTERS                                        | 1             |

| 0x0000 – 0x00FF  | Reserved                                                                 |               |

| 0x0100           | Operation Control Register – Byte 3                                      | 0x00          |

| 0x0101           | Operation Control Register – Byte 2                                      | 0x00          |

| 0x0102           | Reserved                                                                 | 0x00          |

| 0x0103           | Operation Control Register – Byte 0                                      | 0x00          |

| 0x0104           | Operation Status Register – Byte 3 (Device ID)                           | 0xE3          |

| 0x0105           | Operation Status Register – Byte 2 (Revision ID)                         | 0x01          |

| 0x0106 - 0x010A  | Reserved                                                                 | 0x00          |

| 0x010B           | Operation Interrupt Status Register – Byte 0                             | 0x00          |

| 0x010C - 0x010E  | Reserved                                                                 | 0x00          |

| 0x010F           | Operation Interrupt Enable Register – Byte 0                             | 0x00          |

| 0x0110 - 0x0111  | Reserved                                                                 | 0x00          |

| 0x0112           | Operation Block Interrupt Status Register – Byte 1                       | 0x00          |

| 0x0113           | Operation Block Interrupt Status Register – Byte 0                       | 0x00          |

| 0x0114 - 0x0115  | Reserved                                                                 | 0x00          |

| 0x0116           | Operation Block Interrupt Enable Register – Byte 1                       | 0x00          |

| 0x0117           | Operation Block Interrupt Enable Register – Byte 0                       | 0x00          |

| 0x0118 - 0x0119  | Reserved                                                                 | 0x00          |

| 0x011A           | Reserved                                                                 | 0x00          |

| 0x011B           | Mode Control Register – Byte 0                                           | 0x00          |

| 0x011C - 0x011E  | Reserved                                                                 | 0x00          |

| 0x011F           | Loop-back Control Register – Byte 0                                      | 0x00          |

| 0x0120           | Channel Interrupt Indicator Register – Receive SONET POH Processor Block | 0x00          |

| 0x0121           | Reserved                                                                 | 0x00          |

| 0x0122           | Channel Interrupt Indicator Register – DS3/E3 framer Block               | 0x00          |

| 0x0123           | Channel Interrupt Indicator Register – Receive STS-1 POH Processor Block | 0x00          |

| 0x0124           | Channel Interrupt Indicator Register – Receive STS-1 TOH Processor Block | 0x00          |

# 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER - SONET REGISTERS

| 0x0125          | Reserved                                                                             | 0x00 |

|-----------------|--------------------------------------------------------------------------------------|------|

| 0x0126          | Channel Interrupt Indicator Register – STS-1/DS3/E3 Mapper Block                     | 0x00 |

| 0x0127 – 0x0129 | Reserved                                                                             | 0x00 |

| 0x012A - 0x012F | Reserved                                                                             | 0x00 |

| 0x0130 - 0x0131 | Reserved                                                                             | 0x11 |

| 0x0132          | Interface Control Register – Byte 1                                                  | 0x00 |

| 0x0133          | Interface Control Register – Byte 0                                                  | 0x00 |

| 0x0134          | STS-3/STM-1 Telecom Bus Control Register – Byte 3                                    | 0x00 |

| 0x0135          | STS-3/STM-1 Telecom Bus Control Register – Byte 2                                    | 0x00 |

| 0x0136          | Reserved                                                                             | 0x00 |

| 0x0137          | STS-3/STM-1 Telecom Bus Control Register – Byte 0                                    | 0x00 |

| 0x0138          | Reserved                                                                             | 0x00 |

| 0x0139          | Interface Control Register – Byte 2 – STS-3 Telecom Bus 2                            | 0x00 |

| 0x013A          | Interface Control Register – Byte 1 – STS-3 Telecom Bus 1                            | 0x00 |

| 0x013B          | Interface Control Register – Byte 0 – STS-3 Telecom Bus 0                            | 0x00 |

| 0x013C          | Interface Control Register – STS-1 Telecom Bus Interrupt Register                    | 0x00 |

| 0x013D          | Interface Control Register – STS-1 Telecom Bus Interrupt Status Register             | 0x00 |

| 0x013E          | Interface Control Register – STS-1 Telecom Bus Interrupt Register # 2                | 0x00 |

| 0x013F          | Interface Control Register – STS-1 Telecom Bus Interrupt Enable Register             | 0x00 |

| 0x0140 - 0x0146 | Reserved                                                                             | 0x00 |

| 0x0147          | Operation General Purpose Input/Output Register                                      | 0x00 |

| 0x0148 – 0x014A | Reserved                                                                             | 0x00 |

| 0x014B          | Operation General Purpose Input/Output Direction Register – Byte 0                   | 0x00 |

| 0x014C -0x014F  | Reserved                                                                             | 0x00 |

| 0x0150          | Operation Output Control Register – Byte 1                                           | 0x00 |

| 0x0151 -0x0152  | Reserved                                                                             | 0x00 |

| 0x0153          | Operation Output Control Register – Byte 0                                           | 0x00 |

| 0x0154          | Operation Slow Speed Port Control Register – Byte 1                                  | 0x00 |

| 0x0155 – 0x0156 | Reserved                                                                             | 0x00 |

| 0x0157          | Operation Slow Speed Port Control Register –Byte 0                                   | 0x00 |

| 0x0158          | Operation – DS3/E3/STS-1 Clock Frequency Out of Range Detection – Direction Register | 0x00 |

| 0x0159          | Reserved                                                                             | 0x00 |

| 0x015A          | Operation - DS3/E3/STS-1 Clock Frequency - DS3 Out of Range Detection                | 0x00 |

|                 | Threshold Register                                                                            |      |

|-----------------|-----------------------------------------------------------------------------------------------|------|

| 0x015B          | Operation – DS3/E3/STS-1 Clock Frequency – STS-1/E3 Out of Range Detection Threshold Register | 0x00 |

| 0x015C          | Reserved                                                                                      | 0x00 |

| 0x015D          | Operation – DS3/E3/STS-1 Frequency Out of Range Interrupt Enable Register – Byte 0            | 0x00 |

| 0x015E          | Reserved                                                                                      | 0x00 |

| 0x015F          | Operation – DS3/E3/STS-1 Frequency Out of Range Interrupt Status Register – Byte 0            | 0x00 |

| 0x0160 - 0x017F | Reserved                                                                                      | 0x00 |

| 0x0180          | APS Mapping Register                                                                          | 0x00 |

| 0x0181          | APS Control Register                                                                          | 0x00 |

| 0x0182 - 0x0193 | Reserved                                                                                      | 0x00 |

| 0x0194          | APS Status Register                                                                           | 0x00 |

| 0x0195          | Reserved                                                                                      | 0x00 |

| 0x0196          | APS Status Register                                                                           | 0x00 |

| 0x0197          | APS Status Register                                                                           | 0x00 |

| 0x0198          | APS Interrupt Register                                                                        | 0x00 |

| 0x0199          | Reserved                                                                                      | 0x00 |

| 0x019A          | APS Interrupt Register                                                                        | 0x00 |

| 0x019B          | APS Interrupt Register                                                                        | 0x00 |

| 0x019C          | APS Interrupt Register                                                                        | 0x00 |

| 0x019D          | Reserved                                                                                      | 0x00 |

| 0x019E          | APS Interrupt Enable Register                                                                 | 0x00 |

| 0x019F          | APS Interrupt Enable Register                                                                 | 0x00 |

| 0x01A0 - 0x01FF | Reserved                                                                                      | 0x00 |

|                 | LINE INTERFACE CONTROL REGISTERS                                                              |      |

| 0x0302          | Receive Line Interface Control Register – Byte 1                                              | 0x00 |

| 0x0303          | Receive Line Interface Control Register – Byte 0                                              | 0x00 |

| 0x0304 - 0x0306 | Reserved                                                                                      | 0x00 |

| 0x0307          | Receive Line Status Register                                                                  | 0x00 |

| 0x0308 -0x030A  | Reserved                                                                                      | 0x00 |

| 0x030B          | Receive Line Interrupt Register                                                               | 0x00 |

| 0x030C - 0x030E | Reserved                                                                                      | 0x00 |

| 0x030F          | Receive Line Interrupt Enable Register                                                        | 0x00 |

# 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER - SONET REGISTERS

| 0x0310 - 0x0382  | Reserved                                                   | 0x00 |

|------------------|------------------------------------------------------------|------|

| 0x0383           | Transmit Line Interface Control Register                   | 0x00 |

|                  | RECEIVE STS-3 TOH PROCESSOR BLOCK CONTROL REGISTERS        |      |

| 0x1000 – 0x1102  | Reserved                                                   |      |

| 0x1103           | Receive STS-3 Transport Control Register – Byte 0          | 0x00 |

| 0x1104 – 0x1105  | Reserved                                                   | 0x00 |

| 0x1106           | Receive STS-3 Transport Status Register – Byte 1           | 0x00 |

| 0x1107           | Receive STS-3 Transport Status Register – Byte 0           | 0x02 |

| 0x1108           | Reserved                                                   | 0x00 |

| 0x1109           | Receive STS-3 Transport Interrupt Status Register – Byte 2 | 0x00 |

| 0x110A           | Receive STS-3 Transport Interrupt Status Register – Byte 1 | 0x00 |

| 0x110B           | Receive STS-3 Transport Interrupt Status Register – Byte 0 | 0x00 |

| 0x110C           | Reserved                                                   | 0x00 |

| 0x110D           | Receive STS-3 Transport Interrupt Enable Register – Byte 2 | 0x00 |

| 0x110E           | Receive STS-3 Transport Interrupt Enable Register – Byte 1 | 0x00 |

| 0x110F           | Receive STS-3 Transport Interrupt Enable Register – Byte 0 | 0x00 |

| 0x1110           | Receive STS-3 Transport B1 Byte Error Count – Byte 3       | 0x00 |

| 0x1111           | Receive STS-3 Transport B1 Byte Error Count – Byte 2       | 0x00 |

| 0x1112           | Receive STS-3 Transport B1 Byte Error Count – Byte 1       | 0x00 |

| 0x1113           | Receive STS-3 Transport B1 Byte Error Count – Byte 0       | 0x00 |

| 0x1114           | Receive STS-3 Transport B2 Byte Error Count – Byte 3       | 0x00 |

| 0x1115           | Receive STS-3 Transport B2 Byte Error Count – Byte 2       | 0x00 |

| 0x1116           | Receive STS-3 Transport B2 Byte Error Count – Byte 1       | 0x00 |

| 0x1117           | Receive STS-3 Transport B2 Byte Error Count – Byte 0       | 0x00 |

| 0x1118           | Receive STS-3 Transport REI-L Event Count – Byte 3         | 0x00 |

| 0x1119           | Receive STS-3 Transport REI-L Event Count – Byte 2         | 0x00 |

| 0x111A           | Receive STS-3 Transport REI-L Event Count – Byte 1         | 0x00 |

| 0x111B           | Receive STS-3 Transport REI-L Event Count – Byte 0         | 0x00 |

| 0x111C           | Reserved                                                   | 0x00 |

| 0x111D - 0 x111E | Reserved                                                   | 0x00 |

| 0x111F           | Receive STS-3 Transport K1 Byte Value Register             | 0x00 |

| 0x1120 - 0x1122  | Reserved                                                   | 0x00 |

| 0x1123           | Receive STS-3 Transport K2 Byte Value Register             | 0x00 |

| 0x1124 – 0x1126 | Reserved                                                                        | 0x00 |

|-----------------|---------------------------------------------------------------------------------|------|

| 0x1127          | Receive STS-3 Transport S1 Byte Value Register                                  | 0x00 |

| 0x1128 – 0x112A | Reserved                                                                        | 0x00 |

| 0x112B          | Receive STS-3 Transport – In-Sync Threshold Value Register                      | 0x00 |

| 0x112C, 0x112D  | Reserved                                                                        | 0x00 |

| 0x112E          | Receive STS-3 Transport – LOS Threshold Value – MSB                             | 0xFF |

| 0x112F          | Receive STS-3 Transport – LOS Threshold Value – LSB                             | 0xFF |

| 0x1130          | Reserved                                                                        | 0x00 |

| 0x1131          | Receive STS-3 Transport – SF Set Monitor Interval – Byte 2                      | 0x00 |

| 0x1132          | Receive STS-3 Transport – SF Set Monitor Interval – Byte 1                      | 0x00 |

| 0x1133          | Receive STS-3 Transport – SF Set Monitor Interval – Byte 0                      | 0x00 |

| 0x1134 – 0x1135 | Reserved                                                                        | 0x00 |

| 0x1136          | Receive STS-3 Transport – SF Set Threshold – Byte 1                             | 0x00 |

| 0x1137          | Receive STS-3 Transport – SF Set Threshold – Byte 0                             | 0x00 |

| 0x1138, 0x1139  | Reserved                                                                        | 0x00 |

| 0x113A          | Receive STS-3 Transport – SF Clear Threshold – Byte 1                           | 0x00 |

| 0x113B          | Receive STS-3 Transport – SF Clear Threshold – Byte 0                           | 0x00 |

| 0x113C          | Reserved                                                                        | 0x00 |

| 0x113D          | Receive STS-3 Transport – SD Set Monitor Interval – Byte 2                      | 0x00 |

| 0x113E          | Receive STS-3 Transport – SD Set Monitor Interval – Byte 1                      | 0x00 |

| 0x113F          | Receive STS-3 Transport – SD Set Monitor Interval – Byte 0                      | 0x00 |

| 0x1140, 0x1141  | Reserved                                                                        | 0x00 |

| 0x1142          | Receive STS-3 Transport – SD Set Threshold – Byte 1                             | 0x00 |

| 0x1143          | Receive STS-3 Transport – SD Set Threshold – Byte 0                             | 0x00 |

| 0x1144, 0x1145  | Reserved                                                                        | 0x00 |

| 0x1146          | Receive STS-3 Transport – SD Clear Threshold – Byte 1                           | 0x00 |

| 0x1147          | Receive STS-3 Transport – SD Clear Threshold – Byte 0                           | 0x00 |

| 0x1148 – 0x114A | Reserved                                                                        | 0x00 |

| 0x114B          | Receive STS-3 Transport – Force SEF Condition                                   | 0x00 |

| 0x114C, 0x114E  | Reserved                                                                        | 0x00 |

| 0x114F          | Receive STS-3 Transport – Receive Section Trace Message Buffer Control Register | 0x00 |

| 0x1150, 0x1151  | Reserved                                                                        | 0x00 |

| 0x1152          | Receive STS-3 Transport – SD Burst Error Count Tolerance – Byte 1               | 0x00 |

# 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER - SONET REGISTERS

| 0x1153          | Receive STS-3 Transport – SD Burst Error Count Tolerance – Byte 0          | 0x00  |

|-----------------|----------------------------------------------------------------------------|-------|

| 0x1154, 0x1155  | Reserved                                                                   | 0x00  |

| 0x1156          | Receive STS-3 Transport – SF Burst Error Count Tolerance – Byte 1          | 0x00  |

| 0x1157          | Receive STS-3 Transport – SF Burst Error Count Tolerance – Byte 0          | 0x00  |

| 0x1158          | Reserved                                                                   | 0x00  |

| 0x1159          | Receive STS-3 Transport – Receive SD Clear Monitor Interval – Byte 2       | 0xFF  |

| 0x115A          | Receive STS-3 Transport – Receive SD Clear Monitor Interval – Byte 1       | 0xFF  |

| 0x115B          | Receive STS-3 Transport – Receive SD Clear Monitor Interval – Byte 0       | 0xFF  |

| 0x115C          | Reserved                                                                   | 0x00  |

| 0x115D          | Receive STS-3 Transport – Receive SF Clear Monitor Interval – Byte 2       | 0xFF  |

| 0x115E          | Receive STS-3 Transport – Receive SF Clear Monitor Interval – Byte 1       | 0xFF  |

| 0x115F          | Receive STS-3 Transport – Receive SF Clear Monitor – Byte 0                | 0xFF  |

| 0x1160 - 0x1162 | Reserved                                                                   | 0x00  |

| 0x1163          | Receive STS-3 Transport – Auto AIS Control Register                        | 0x00  |

| 0x1164 – 0x1166 | Reserved                                                                   | 0x00  |

| 0x1167          | Receive STS-3 Transport – Serial Port Control Register                     | 0x00  |

| 0x1168 – 0x116A | Reserved                                                                   | 0x00  |

| 0x116B          | Receive STS-3 Transport – Auto AIS (in Downstream STS-1s) Control Register | 0x000 |

| 0x116C - 0x1179 | Reserved                                                                   | 0x00  |

| 0x117A          | Receive STS-3 Transport – TOH Capture Indirect Address                     | 0x00  |

| 0x117B          | Receive STS-3 Transport – TOH Capture Indirect Address                     | 0x00  |

| 0x117C          | Receive STS-3 Transport – TOH Capture Indirect Data                        | 0x00  |

| 0x117D          | Receive STS-3 Transport – TOH Capture Indirect Data                        | 0x00  |

| 0x117E          | Receive STS-3 Transport – TOH Capture Indirect Data                        | 0x00  |

| 0x117F          | Receive STS-3 Transport – TOH Capture Indirect Data                        | 0x00  |

| 0x1180          | Reserved                                                                   | 0x00  |

|                 | RECEIVE STS-3c POH PROCESSOR BLOCK                                         | 1     |

| 0x1181          | Reserved                                                                   | 0x00  |

| 0x1182          | Receive STS-3c Path – Control Register – Byte 1                            | 0x00  |

| 0x1183          | Receive STS-3c Path – Control Register – Byte 0                            | 0x00  |

| 0x1184 – 0x1185 | Reserved                                                                   | 0x00  |

| 0x1186          | Receive STS-3c Path – Status Register – Byte 1                             | 0x00  |

| 0x1187          | Receive STS-3c Path – Status Register – Byte 0                             | 0x00  |

| 0x1188          | Reserved                                                               | 0x00 |

|-----------------|------------------------------------------------------------------------|------|

| 0x1189          | Receive STS-3c Path – Interrupt Status Register – Byte 2               | 0x00 |

| 0x118A          | Receive STS-3c Path – Interrupt Status Register – Byte 1               | 0x00 |

| 0x118B          | Receive STS-3c Path – Interrupt Status Register – Byte 0               | 0x00 |

| 0x118C          | Reserved                                                               | 0x00 |

| 0x118D          | Receive STS-3c Path – Interrupt Enable Register – Byte 2               | 0x00 |

| 0x118E          | Receive STS-3c Path – Interrupt Enable Register – Byte 1               | 0x00 |

| 0x118F          | Receive STS-3c Path – Interrupt Enable Register – Byte 0               | 0x00 |

| 0x1190 – 0x1192 | Reserved                                                               | 0x00 |

| 0x1193          | Receive STS-3c Path – SONET Receive RDI-P Register                     | 0x00 |

| 0x1194 – 0x1195 | Reserved                                                               | 0x00 |

| 0x1196          | Receive STS-3c Path – Receive Path Label Byte (C2) Byte Register       | 0x00 |

| 0x1197          | Receive STS-3c Path – Expected Path Label Byte (C2) Byte Register      | 0x00 |

| 0x1198          | Receive STS-3c Path – B3 Byte Error Count Register – Byte 3            | 0x00 |

| 0x1199          | Receive STS-3c Path – B3 Byte Error Count Register – Byte 2            | 0x00 |

| 0x119A          | Receive STS-3c Path – B3 Byte Error Count Register – Byte 1            | 0x00 |

| 0x119B          | Receive STS-3c Path – B3 Byte Error Count Register – Byte 0            | 0x00 |

| 0x119C          | Receive STS-3c Path – REI-P Event Count Register – Byte 3              | 0x00 |

| 0x119D          | Receive STS-3c Path – REI-P Event Count Register – Byte 2              | 0x00 |

| 0x119E          | Receive STS-3c Path – REI-P Event Count Register – Byte 1              | 0x00 |

| 0x119F          | Receive STS-3c Path – REI-P Event Count Register – Byte 0              | 0x00 |

| 0x11A0 - 0x11A2 | Reserved                                                               | 0x00 |

| 0x11A3          | Receive STS-3c Path – Receive Path Trace Message Byte Control Register | 0x00 |

| 0x11A4 – 0x11A5 | Reserved                                                               | 0x00 |

| 0x11A6          | Receive STS-3c Path – Pointer Value Register – Byte 1                  | 0x00 |

| 0x11A7          | Receive STS-3c Path – Pointer Value Register – Byte 0                  | 0x00 |

| 0x11A8 - 0x11AA | Reserved                                                               | 0x00 |

| 0x11AB          | Receive STS-3c Path – Loss of Pointer – Concatenation Status Register  | 0x00 |

| 0x11AC - 0x11B2 | Reserved                                                               | 0x00 |

| 0x11B3          | Receive STS-3c Path – AIS – Concatenation Status Register              | 0x00 |

| 0x11B4 - 0x11BA | Reserved                                                               | 0x00 |

| 0x11BB          | Receive STS-3c Path – Auto AIS Control Register                        | 0x00 |

| 0x11BC - 0x11BE | Reserved                                                               | 0x00 |

# EXAR Experience Our Connectivity

# 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER - SONET REGISTERS

| 0x11BF          | Receive STS-3c Path – Serial Port Control Register                                                          | 0x00   |

|-----------------|-------------------------------------------------------------------------------------------------------------|--------|

| 0x11C0 - 0x11C2 | Reserved                                                                                                    | 0x00   |

| 0x11C3          | Receive STS-3c Path - Receive SONET Auto Alarm Register – Byte 0                                            | 0x00   |

| 0x11C4 -0x11D2  | Reserved                                                                                                    | 0x00   |

| 0x11D3          | Receive STS-3c Path – Receive J1 Byte Capture Register                                                      | 0x00   |

| 0x11D4 – 0x11D6 | Reserved                                                                                                    | 0x00   |

| 0x11D7          | Receive STS-3c Path – Receive B3 Byte Capture Register                                                      | 0x00   |

| 0x11D8 – 0x11DA | Reserved                                                                                                    | 0x00   |

| 0x11DB          | Receive STS-3c Path – Receive C2 Byte Capture Register                                                      | 0x00   |

| 0x11DC - 0x11DE | Reserved                                                                                                    | 0x00   |

| 0x11DF          | Receive STS-3c Path – Receive G1 Byte Capture Register                                                      | 0x00   |

| 0x11E0 - 0x11E2 | Reserved                                                                                                    | 0x00   |

| 0x11E3          | Receive STS-3c Path – Receive F2 Byte Capture Register                                                      | 0x00   |

| 0x11E4 - 0x11E6 | Reserved                                                                                                    | 0x00   |

| 0x11E7          | Receive STS-3c Path – Receive H4 Byte Capture Register                                                      | 0x00   |

| 0x11E8 - 0x11EA | Reserved                                                                                                    | 0x00   |

| 0x11EB          | Receive STS-3c Path – Receive Z3 Byte Capture Register                                                      | 0x00   |

| 0x11EC - 0x11EE | Reserved                                                                                                    | 0x00   |

| 0x11EF          | Receive STS-3c Path – Receive Z4 (K3) Byte Capture Register                                                 | 0x00   |

| 0x11F0 - 0x11F2 | Reserved                                                                                                    | 0x00   |

| 0x11F3          | Receive STS-3c Path – Receive Z5 Byte Capture Register                                                      | 0x00   |

| 0x11F4 - 0x12FF | Reserved                                                                                                    | 0x00   |

| RECEIVE         | STS-3/STM-1 TOH PROCESSOR BLOCK - RECEIVE JO (SECTION) TRACE MESSAGE E                                      | BUFFER |

| 0x1300 – 0x133F | Receive STS-3/STM-1 TOH Processor Block – Receive J0 (Section) Trace Message Buffer – Expected and Received | 0x00   |

| 0x1340 – 0x13FF | Reserved                                                                                                    | 0x00   |

| Receive         | STS-3c POH Processor Block – Receive J1 (PATH) Trace Message Buffer – S                                     | TS-3c  |

| 0x1500 - 0x153F | Receive STS-3c POH Processor Block – Receive J1 (Path) Trace Message Buffer                                 | 0x00   |

| 0x1540 – 0x15FF | Reserved                                                                                                    | 0x00   |

|                 | REDUNDANT RECEIVE STS-3 TOH PROCESSOR BLOCK CONTROL REGISTERS                                               |        |

| 0x1600 - 0x1702 | Reserved                                                                                                    |        |

| 0x1703          | Redundant Receive STS-3 Transport Control Register – Byte 0                                                 | 0x00   |

| 0x1704 – 0x1705 | Reserved                                                                                                    | 0x00   |

| 0x1706          | Redundant Receive STS-3 Transport Status Register – Byte 1                                                  | 0x00   |

|                 | 1                                                                                                           |        |

| 0x1707              | Redundant Receive STS-3 Transport Status Register – Byte 0           | 0x02 |

|---------------------|----------------------------------------------------------------------|------|

| 0x1708              | Reserved                                                             | 0x00 |

| 0x1709              | Redundant Receive STS-3 Transport Interrupt Status Register – Byte 2 | 0x00 |

| 0x170A              | Redundant Receive STS-3 Transport Interrupt Status Register – Byte 1 | 0x00 |

| 0x170B              | Redundant Receive STS-3 Transport Interrupt Status Register – Byte 0 | 0x00 |

| 0x170C              | Reserved                                                             | 0x00 |

| 0x170D              | Redundant Receive STS-3 Transport Interrupt Enable Register – Byte 2 | 0x00 |

| 0x170E              | Redundant Receive STS-3 Transport Interrupt Enable Register – Byte 1 | 0x00 |

| 0x170F              | Redundant Receive STS-3 Transport Interrupt Enable Register – Byte 0 | 0x00 |

| 0x1710              | Redundant Receive STS-3 Transport B1 Byte Error Count – Byte 3       | 0x00 |

| 0x1711              | Redundant Receive STS-3 Transport B1 Byte Error Count – Byte 2       | 0x00 |

| 0x1712              | Redundant Receive STS-3 Transport B1 Byte Error Count – Byte 1       | 0x00 |

| 0x1713              | Redundant Receive STS-3 Transport B1 Byte Error Count – Byte 0       | 0x00 |

| 0x1714              | Redundant Receive STS-3 Transport B2 Byte Error Count – Byte 3       | 0x00 |

| 0x1715              | Redundant Receive STS-3 Transport B2 Byte Error Count – Byte 2       | 0x00 |

| 0x1716              | Redundant Receive STS-3 Transport B2 Byte Error Count – Byte 1       | 0x00 |

| 0x1717              | Redundant Receive STS-3 Transport B2 Byte Error Count – Byte 0       | 0x00 |

| 0x1718              | Redundant Receive STS-3 Transport REI-L Event Count – Byte 3         | 0x00 |

| 0x1719              | Redundant Receive STS-3 Transport REI-L Event Count – Byte 2         | 0x00 |

| 0x171A              | Redundant Receive STS-3 Transport REI-L Event Count – Byte 1         | 0x00 |

| 0x171B              | Redundant Receive STS-3 Transport REI-L Event Count – Byte 0         | 0x00 |

| 0x171C -<br>0 x171E | Reserved                                                             | 0x00 |

| 0x171F              | Redundant Receive STS-3 Transport K1 Byte Value Register             | 0x00 |

| 0x1720 - 0x1722     | Reserved                                                             | 0x00 |

| 0x1723              | Redundant Receive STS-3 Transport K2 Byte Value Register             | 0x00 |

| 0x1724 - 0x1726     | Reserved                                                             | 0x00 |

| 0x1727              | Redundant Receive STS-3 Transport S1 Byte Value Register             | 0x00 |

| 0x1728 - 0x172A     | Reserved                                                             | 0x00 |

| 0x172B              | Redundant Receive STS-3 Transport – In-Sync Threshold Value          | 0x00 |

| 0x172C, 0x172D      | Reserved                                                             | 0x00 |

| 0x172E              | Redundant Receive STS-3 Transport – LOS Threshold Value – MSB        | 0xFF |

| 0x172F              | Redundant Receive STS-3 Transport – LOS Threshold Value – LSB        | 0xFF |

| 0x1730              | Reserved                                                             | 0x00 |

# 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER - SONET REGISTERS

| 0x1731          | Redundant Receive STS-3 Transport – SF Set Monitor Interval – Byte 2           | 0x00 |

|-----------------|--------------------------------------------------------------------------------|------|

| 0x1732          | Redundant Receive STS-3 Transport – SF Set Monitor Interval – Byte 1           | 0x00 |

| 0x1733          | Redundant Receive STS-3 Transport – SF Set Monitor Interval – Byte 0           | 0x00 |

| 0x1734 - 0x1735 | Reserved                                                                       | 0x00 |

| 0x1736          | Redundant Receive STS-3 Transport – SF Set Threshold – Byte 1                  | 0x00 |

| 0x1737          | Redundant Receive STS-3 Transport – SF Set Threshold – Byte 0                  | 0x00 |

| 0x1738, 0x1739  | Reserved                                                                       | 0x00 |

| 0x173A          | Redundant Receive STS-3 Transport – SF Clear Threshold – Byte 1                | 0x00 |

| 0x173B          | Redundant Receive STS-3 Transport – SF Clear Threshold – Byte 0                | 0x00 |

| 0x173C          | Reserved                                                                       | 0x00 |

| 0x173D          | Redundant Receive STS-3 Transport – SD Set Monitor Interval – Byte 2           | 0x00 |

| 0x173E          | Redundant Receive STS-3 Transport – SD Set Monitor Interval – Byte 1           | 0x00 |

| 0x173F          | Redundant Receive STS-3 Transport – SD Set Monitor Interval – Byte 0           | 0x00 |

| 0x1740, 0x1741  | Reserved                                                                       | 0x00 |

| 0x1742          | Redundant Receive STS-3 Transport – SD Set Threshold – Byte 1                  | 0x00 |

| 0x1743          | Redundant Receive STS-3 Transport – SD Set Threshold – Byte 0                  | 0x00 |

| 0x1744, 0x1745  | Reserved                                                                       | 0x00 |

| 0x1746          | Redundant Receive STS-3 Transport – SD Clear Threshold – Byte 1                | 0x00 |

| 0x1747          | Redundant Receive STS-3 Transport – SD Clear Threshold – Byte 0                | 0x00 |

| 0x1748 – 0x174A | Reserved                                                                       | 0x00 |

| 0x174B          | Redundant Receive STS-3 Transport – Force SEF Condition                        | 0x00 |

| 0x174C, 0x1751  | Reserved                                                                       | 0x00 |

| 0x1752          | Redundant Receive STS-3 Transport – SD Burst Error Count Tolerance – Byte 1    | 0x00 |

| 0x1753          | Redundant Receive STS-3 Transport – SD Burst Error Count Tolerance – Byte 0    | 0x00 |

| 0x1754, 0x1755  | Reserved                                                                       | 0x00 |

| 0x1756          | Redundant Receive STS-3 Transport – SF Burst Error Count Tolerance – Byte 1    | 0x00 |

| 0x1757          | Redundant Receive STS-3 Transport – SF Burst Error Count Tolerance – Byte 0    | 0x00 |

| 0x1758          | Reserved                                                                       | 0x00 |

| 0x1759          | Redundant Receive STS-3 Transport – Receive SD Clear Monitor Interval – Byte 2 | 0xFF |

| 0x175A          | Redundant Receive STS-3 Transport - Receive SD Clear Monitor Interval - Byte 1 | 0xFF |

| 0x175B          | Redundant Receive STS-3 Transport – Receive SD Clear Monitor Interval – Byte 0 | 0xFF |

|-----------------|--------------------------------------------------------------------------------|------|

| 0x175C          | Reserved                                                                       | 0x00 |

| 0x175D          | Redundant Receive STS-3 Transport – Receive SF Clear Monitor Interval – Byte 2 | 0xFF |

| 0x175E          | Redundant Receive STS-3 Transport – Receive SF Clear Monitor Interval – Byte 1 | 0xFF |

| 0x175F          | Redundant Receive STS-3 Transport – Receive SF Clear Monitor – Byte 0          | 0xFF |

| 0x1760 - 0x1766 | Reserved                                                                       | 0x00 |

| 0x1767          | Redundant Receive STS-3 Transport – Serial Port Control Register               | 0x00 |

| 0x1768 – 0x1779 | Reserved                                                                       | 0x00 |

| 0x177A          | Redundant Receive STS-3 Transport – TOH Capture Indirect Address               | 0x00 |

| 0x177B          | Redundant Receive STS-3 Transport – TOH Capture Indirect Address               | 0x00 |

| 0x177C          | Redundant Receive STS-3 Transport – TOH Capture Indirect Data                  | 0x00 |

| 0x177D          | Redundant Receive STS-3 Transport – TOH Capture Indirect Data                  | 0x00 |

| 0x177E          | Redundant Receive STS-3 Transport – TOH Capture Indirect Data                  | 0x00 |

| 0x177F          | Redundant Receive STS-3 Transport – TOH Capture Indirect Data                  | 0x00 |

| 0x1780 – 0x17FF | Reserved                                                                       | 0x00 |

|                 | TRANSMIT STS-3 TOH PROCESSOR BLOCK CONTROL REGISTERS                           |      |

| 0x1800 - 0x1901 | Reserved                                                                       | 0x00 |

| 0x1902          | Transmit STS-3 Transport – SONET Transmit Control Register – Byte 1            | 0x00 |

| 0x1903          | Transmit STS-3 Transport – SONET Transmit Control Register – Byte 0            | 0x00 |

| 0x1904 - 0x1916 | Reserved                                                                       | 0x00 |

| 0x1917          | Transmit STS-3 Transport – Transmit A1 Error Mask – Low Register – Byte 0      | 0x00 |

| 0x1918 - 0x191E | Reserved                                                                       | 0x00 |

| 0x191F          | Transmit STS-3 Transport – Transmit A2 Error Mask – Low Register – Byte 0      | 0x00 |

| 0x1920 - 0x1921 | Reserved                                                                       | 0x00 |

| 0x1923          | Transmit STS-3 Transport – B1 Byte Error Mask Register                         | 0x00 |

| 0x1924 - 0x1926 | Reserved                                                                       | 0x00 |

| 0x1927          | Transmit STS-3 Transport – Transmit B2 Byte Error Mask Register – Byte 0       | 0x00 |

| 0x1928 – 0x192A | Reserved                                                                       | 0x00 |

| 0x192B          | Transmit STS-3 Transport – Transmit B2 Bit Error Mask Register – Byte 0        | 0x00 |

| 0x192C - 0x192D | Reserved                                                                       | 0x00 |

| 0x192E          | Transmit STS-3 Transport – K1K2 (APS) Byte Value Register – Byte 1             | 0x00 |

| 0x192F          | Transmit STS-3 Transport – K1K2 (APS) Byte Value Register – Byte 0             | 0x00 |

# 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER - SONET REGISTERS

| 0x1930 – 0x1931    | Reserved                                                | 0x00     |

|--------------------|---------------------------------------------------------|----------|

| 0x1933             | Transmit STS-3 Transport – RDI-L Control Register       | 0x00     |

| 0x1934 - 0x1936    | Reserved                                                | 0x00     |

| 0x1937             | Transmit STS-3 Transport – M0M1 Byte Value Register     | 0x00     |

| 0x1938 –<br>0x193A | Reserved                                                | 0x00     |

| 0x193B             | Transmit STS-3 Transport – S1 Byte Value Register       | 0x00     |

| 0x193C - 0x193E    | Reserved                                                | 0x00     |

| 0x193F             | Transmit STS-3 Transport – F1 Byte Value Register       | 0x00     |

| 0x1940 - 0x1942    | Reserved                                                | 0x00     |

| 0x1943 - 0x1946    | Transmit STS-3 Transport – E1 Byte Value Register       | 0x00     |

| 0x1947             | Transmit STS-3 Transport – E2 Byte Value Register       | 0x00     |

| 0x1948 – 0x194A    | Reserved                                                | 0x00     |

| 0x194B             | Transmit STS-3 Transport – J0 Byte Value Register       | 0x00     |

| 0x194C - 0x194E    | Reserved                                                | 0x00     |

| 0x194F             | Transmit STS-3 Transport – J0 Byte Control Register     | 0x00     |

| 0x1950 - 0x1952    | Reserved                                                | 0x00     |

| 0x1953             | Transmit STS-3 Transport – Serial Port Control Register | 0x00     |

| 0x1954 -0x1980     | Reserved                                                | 0x00     |

|                    | TRANSMIT STS-3c POH PROCESSOR BLOCK                     | <b>1</b> |

| 0x1981             | Reserved                                                | 0x00     |

| 0x1982             | Transmit STS-3c Path – SONET Control Register – Byte 1  | 0x00     |

| 0x1983             | Transmit STS-3c Path – SONET Control Register- Byte 0   | 0x00     |

| 0x1984 - 0x1992    | Reserved                                                | 0x00     |

| 0x1993             | Transmit STS-3c Path – Transmit J1 Byte Value Register  | 0x00     |

| 0x1994 – 0x1996    | Reserved                                                | 0x00     |

| 0x1997             | Transmit STS-3c Path – B3 Byte Mask Register            | 0x00     |

| 0x1998 – 0x199A    | Reserved                                                | 0x00     |

| 0x199B             | Transmit STS-3c Path – Transmit C2 Byte Value Register  | 0x00     |

| 0x199C - 0x199E    | Reserved                                                | 0x00     |

| 0x199F             | Transmit STS-3c Path – Transmit G1 Byte Value Register  | 0x00     |

| 0x19A0 - 0x19A2    | Reserved                                                | 0x00     |

| 0x19A3             | Transmit STS-3c Path – Transmit F2 Byte Value Register  | 0x00     |

| 0x19A4 -0x19A6     | Reserved                                                | 0x00     |

| 0x19AC - 0x19AE         Rese           0x19AF         Trans           0x19B0 - 0x19B2         Rese           0x19B3         Trans           0x19B4 - 0x19B6         Rese           0x19B7         Trans           0x19B8 - 0x19BA         Rese           0x19BB         Trans           0x19BC -0x19BE         Rese           0x19BF         Trans           0x19C0 - 0x19C2         Rese           0x19C3         Trans           0x19C4 - 0x19C5         Rese           0x19C6         Trans           0x19C7         Trans           0x19C8         Rese           0x19C9         Trans           0x19CA         Trans           0x19CB         Trans           0x19CC -0x19CE         Rese | smit STS-3c Path – Transmit Z3 Byte Value Register  rived  smit STS-3c Path – Transmit Z4 Byte Value Register  rived  smit STS-3c Path – Transmit Z5 Byte Value Register  rived  smit STS-3c Path – Transmit Path Control Register – Byte 0  rived  smit STS-3c Path – Transmit J1 Byte Control Register  rived  smit STS-3c Path – Transmit Arbitrary H1 Byte Pointer Register  rived  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rived  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rived  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rived  smit STS-3c Path – Transmit Pointer Byte Register –Byte 1    | 0x00 0x00 0x00 0x00 0x00 0x00 0x00 0x0               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 0x19AC - 0x19AE Rese 0x19AF Trans 0x19B0 - 0x19B2 Rese 0x19B3 Trans 0x19B4 - 0x19B6 Rese 0x19B7 Trans 0x19B8 - 0x19BA Rese 0x19BB Trans 0x19BC -0x19BE Rese 0x19BF Trans 0x19C0 - 0x19C2 Rese 0x19C3 Trans 0x19C4 - 0x19C5 Rese 0x19C6 Trans 0x19C7 Trans 0x19C8 Rese 0x19C9 Trans 0x19CA Trans 0x19CA Trans 0x19CB Rese                                                                                                                                                                                                                                                                                                                                                                       | smit STS-3c Path – Transmit Z4 Byte Value Register  rved  smit STS-3c Path – Transmit Z5 Byte Value Register  rved  smit STS-3c Path – Transmit Path Control Register – Byte 0  rved  smit STS-3c Path – Transmit J1 Byte Control Register  rved  smit STS-3c Path – Transmit Arbitrary H1 Byte Pointer Register  rved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rved  smit STS-3c Path – Transmit Pointer Byte Register –Byte 1 | 0x00 0x00 0x00 0x00 0x00 0x00 0x00 0x0               |

| 0x19AF         Trans           0x19B0 – 0x19B2         Rese           0x19B3         Trans           0x19B4 – 0x19B6         Rese           0x19B7         Trans           0x19B8 – 0x19BA         Rese           0x19BB         Trans           0x19BC –0x19BE         Rese           0x19BF         Trans           0x19C0 – 0x19C2         Rese           0x19C3         Trans           0x19C4 – 0x19C5         Rese           0x19C6         Trans           0x19C7         Trans           0x19C8         Rese           0x19C9         Trans           0x19CA         Trans           0x19CB         Trans           0x19CC –0x19CE         Rese                                        | smit STS-3c Path – Transmit Z4 Byte Value Register  sreved  smit STS-3c Path – Transmit Z5 Byte Value Register  sreved  smit STS-3c Path – Transmit Path Control Register – Byte 0  sreved  smit STS-3c Path – Transmit J1 Byte Control Register  sreved  smit STS-3c Path – Transmit Arbitrary H1 Byte Pointer Register  sreved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  sreved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  sreved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  sreved  smit STS-3c Path – Transmit Pointer Byte Register –Byte 1                                                       | 0x00 0x00 0x00 0x00 0x00 0x00 0x00 0x0               |

| 0x19B0 – 0x19B2 Rese 0x19B3 Trans 0x19B4 – 0x19B6 Rese 0x19B7 Trans 0x19B8 – 0x19BA Rese 0x19BB Trans 0x19BC –0x19BE Rese 0x19BF Trans 0x19C0 – 0x19C2 Rese 0x19C3 Trans 0x19C4 – 0x19C5 Rese 0x19C6 Trans 0x19C7 Trans 0x19C8 Rese 0x19C9 Trans 0x19CA Trans 0x19CA Trans 0x19CA Trans 0x19CB Rese                                                                                                                                                                                                                                                                                                                                                                                            | smit STS-3c Path – Transmit Z5 Byte Value Register  sred  smit STS-3c Path – Transmit Path Control Register – Byte 0  sred  smit STS-3c Path – Transmit J1 Byte Control Register  sred  smit STS-3c Path – Transmit Arbitrary H1 Byte Pointer Register  sred  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  sred  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  sred  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  sred  smit STS-3c Path – Transmit Pointer Byte Register –Byte 1                                                                                                                                 | 0x00 0x00 0x00 0x00 0x00 0x00 0x00 0x0               |

| 0x19B3         Trans           0x19B4 – 0x19B6         Rese           0x19B7         Trans           0x19B8 – 0x19BA         Rese           0x19BB         Trans           0x19BC –0x19BE         Rese           0x19BF         Trans           0x19C0 – 0x19C2         Rese           0x19C3         Trans           0x19C4 – 0x19C5         Rese           0x19C6         Trans           0x19C7         Trans           0x19C8         Rese           0x19C9         Trans           0x19CA         Trans           0x19CB         Trans           0x19CC –0x19CE         Rese                                                                                                              | smit STS-3c Path – Transmit Z5 Byte Value Register  rved  smit STS-3c Path – Transmit Path Control Register – Byte 0  rved  smit STS-3c Path- Transmit J1 Byte Control Register  rved  smit STS-3c Path – Transmit Arbitrary H1 Byte Pointer Register  rved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rved  smit STS-3c Path – Transmit Pointer Byte Register – Byte 1                                                                                                                                 | 0x00 0x00 0x00 0x00 0x00 0x00 0x00 0x0               |

| 0x19B4 - 0x19B6         Rese           0x19B7         Trans           0x19B8 - 0x19BA         Rese           0x19BB         Trans           0x19BC -0x19BE         Rese           0x19BF         Trans           0x19C0 - 0x19C2         Rese           0x19C3         Trans           0x19C4 - 0x19C5         Rese           0x19C6         Trans           0x19C7         Trans           0x19C8         Rese           0x19C9         Trans           0x19CA         Trans           0x19CB         Trans           0x19CC -0x19CE         Rese                                                                                                                                             | smit STS-3c Path – Transmit Path Control Register – Byte 0 smit STS-3c Path- Transmit J1 Byte Control Register srved smit STS-3c Path – Transmit Arbitrary H1 Byte Pointer Register srved smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register srved smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register srved smit STS-3c Path – Transmit Pointer Byte Register –Byte 1                                                                                                                                                                                                                                                                             | 0x00 0x00 0x00 0x00 0x00 0x00 0x00 0x0               |

| 0x19B7         Trans           0x19B8 – 0x19BA         Rese           0x19BB         Trans           0x19BC –0x19BE         Rese           0x19BF         Trans           0x19C0 – 0x19C2         Rese           0x19C3         Trans           0x19C4 – 0x19C5         Rese           0x19C6         Trans           0x19C7         Trans           0x19C8         Rese           0x19C9         Trans           0x19CA         Trans           0x19CB         Trans           0x19CC –0x19CE         Rese                                                                                                                                                                                    | smit STS-3c Path – Transmit Path Control Register – Byte 0 srived smit STS-3c Path- Transmit J1 Byte Control Register srived smit STS-3c Path – Transmit Arbitrary H1 Byte Pointer Register srived smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register srived smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register srived smit STS-3c Path – Transmit Pointer Byte Register –Byte 1                                                                                                                                                                                                                                                                  | 0x00 0x00 0x00 0x00 0x00 0x00 0x00 0x0               |

| 0x19B8 – 0x19BA Rese 0x19BB Trans 0x19BC –0x19BE Rese 0x19BF Trans 0x19C0 – 0x19C2 Rese 0x19C3 Trans 0x19C4 – 0x19C5 Rese 0x19C6 Trans 0x19C7 Trans 0x19C8 Rese 0x19C9 Trans 0x19C9 Trans 0x19CA Trans 0x19CA Trans 0x19CB Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                | smit STS-3c Path- Transmit J1 Byte Control Register  rved  smit STS-3c Path – Transmit Arbitrary H1 Byte Pointer Register  rved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rved  smit STS-3c Path – Transmit Pointer Byte Register –Byte 1                                                                                                                                                                                                                                                                                                                                    | 0x00<br>0x00<br>0x00<br>0x00<br>0x00<br>0x00<br>0x00 |

| 0x19BB         Trans           0x19BC -0x19BE         Rese           0x19BF         Trans           0x19C0 - 0x19C2         Rese           0x19C3         Trans           0x19C4 - 0x19C5         Rese           0x19C6         Trans           0x19C7         Trans           0x19C8         Rese           0x19C9         Trans           0x19CA         Trans           0x19CB         Trans           0x19CC -0x19CE         Rese                                                                                                                                                                                                                                                          | smit STS-3c Path- Transmit J1 Byte Control Register  rved  smit STS-3c Path – Transmit Arbitrary H1 Byte Pointer Register  rved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rved  smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rved  smit STS-3c Path – Transmit Pointer Byte Register –Byte 1                                                                                                                                                                                                                                                                                                                                    | 0x00<br>0x00<br>0x00<br>0x00<br>0x00<br>0x00         |

| 0x19BC -0x19BE         Rese           0x19BF         Trans           0x19C0 - 0x19C2         Rese           0x19C3         Trans           0x19C4 - 0x19C5         Rese           0x19C6         Trans           0x19C7         Trans           0x19C8         Rese           0x19C9         Trans           0x19CA         Trans           0x19CB         Trans           0x19CC -0x19CE         Rese                                                                                                                                                                                                                                                                                         | smit STS-3c Path – Transmit Arbitrary H1 Byte Pointer Register rved smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register rved smit STS-3c Path – Transmit Pointer Byte Register –Byte 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x00<br>0x00<br>0x00<br>0x00<br>0x00<br>0x00         |

| 0x19BF         Trans           0x19C0 – 0x19C2         Rese           0x19C3         Trans           0x19C4 – 0x19C5         Rese           0x19C6         Trans           0x19C7         Trans           0x19C8         Rese           0x19C9         Trans           0x19CA         Trans           0x19CB         Trans           0x19CB         Trans           0x19CC –0x19CE         Rese                                                                                                                                                                                                                                                                                                | smit STS-3c Path – Transmit Arbitrary H1 Byte Pointer Register  rved smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register  rved smit STS-3c Path – Transmit Pointer Byte Register –Byte 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x00<br>0x00<br>0x00<br>0x00<br>0x00                 |

| 0x19C0 - 0x19C2 Rese 0x19C3 Trans 0x19C4 - 0x19C5 Rese 0x19C6 Trans 0x19C7 Trans 0x19C8 Rese 0x19C9 Trans 0x19C9 Trans 0x19CA Trans 0x19CB Trans 0x19CB Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register rved smit STS-3c Path – Transmit Pointer Byte Register –Byte 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x00<br>0x00<br>0x00<br>0x00                         |

| 0x19C3       Trans         0x19C4 – 0x19C5       Rese         0x19C6       Trans         0x19C7       Trans         0x19C8       Rese         0x19C9       Trans         0x19CA       Trans         0x19CB       Trans         0x19CC –0x19CE       Rese                                                                                                                                                                                                                                                                                                                                                                                                                                       | smit STS-3c Path – Transmit Arbitrary H2 Byte Pointer Register rved smit STS-3c Path – Transmit Pointer Byte Register –Byte 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x00<br>0x00<br>0x00                                 |

| 0x19C4 - 0x19C5 Rese 0x19C6 Trans 0x19C7 Trans 0x19C8 Rese 0x19C9 Trans 0x19CA Trans 0x19CA Trans 0x19CB Trans 0x19CB Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | rved smit STS-3c Path – Transmit Pointer Byte Register –Byte 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x00<br>0x00                                         |

| 0x19C6         Trans           0x19C7         Trans           0x19C8         Rese           0x19C9         Trans           0x19CA         Trans           0x19CB         Trans           0x19CC -0x19CE         Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | smit STS-3c Path – Transmit Pointer Byte Register –Byte 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x00                                                 |

| 0x19C7         Trans           0x19C8         Rese           0x19C9         Trans           0x19CA         Trans           0x19CB         Trans           0x19CC -0x19CE         Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      |

| 0x19C8         Rese           0x19C9         Trans           0x19CA         Trans           0x19CB         Trans           0x19CC -0x19CE         Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | amit CTC 2a Dath - Transmit Daintar Puta Dagistar - Puta 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x00                                                 |

| 0x19C9         Trans           0x19CA         Trans           0x19CB         Trans           0x19CC -0x19CE         Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | smit STS-3c Path – Transmit Pointer Byte Register – Byte 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0,00                                                 |

| 0x19CA Trans 0x19CB Trans 0x19CC -0x19CE Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | rved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x00                                                 |

| 0x19CB Trans 0x19CC -0x19CE Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | smit STS-3c Path – RDI-P Control Register – Byte 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x00                                                 |